# **ECE/CS 252: INTRODUCTION TO COMPUTER ENGINEERING**

## UNIVERSITY OF WISCONSIN—MADISON

Prof. Mikko Lipasti & Prof. Gurinder S. Sohi

TAs: Felix Loh, Daniel Chang, Philip Garcia, Sean Franey, Vignyan Kothinti Naresh, Raghu Raman and Newsha Ardalani

Midterm Examination 2

In Class (50 minutes)

Friday, October 22, 2010

Weight: 12.5%

#### NO: BOOK(S), NOTE(S), CALCULATORS OF ANY SORT.

This exam has ten pages, including two blank pages at the end. Plan your time carefully, since some problems are longer than others. You must turn in pages 1 to 8.

| LAST NAME:     | Solution Key |  |

|----------------|--------------|--|

| FIRST NAME:    |              |  |

| IIIOI IVAIVIL. |              |  |

| SECTION:       |              |  |

| ID#            |              |  |

| Problem | Maximum Points | Actual Points |

|---------|----------------|---------------|

| 1       | 4              |               |

| 2       | 3              |               |

| 3       | 4              |               |

| 4       | 4              |               |

| 5       | 6              |               |

| 6       | 4              |               |

| Total   | 25             |               |

### Problem 1 (4 Points)

Write the Boolean expression for the output Z, as a function of the inputs A, B, and C, corresponding to the following truth table. You need not simplify the expression.

|   | Inputs |   |   |

|---|--------|---|---|

| Α | В      | С | Z |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 0 |

| 1 | 1      | 0 | 0 |

| 1 | 1      | 1 | 1 |

Z = [(NOT A) AND B AND C] OR [A AND (NOT B) AND (NOT C)] OR [A AND B AND C]

#### Problem 2 (3 Points)

Suppose a 32-bit instruction takes the following format:

| OPCODE | DR | SR1 | SR2 | UNUSED |

|--------|----|-----|-----|--------|

|        |    |     |     |        |

If there are 320 opcodes:

a) What is the minimum number of bits required to represent the OPCODE?

9 bits

**b)** What is the maximum possible number of registers? Show your work.

We have 32 - 9 = 23 bits remaining. The DR, SR1 and SR2 fields need to have the same number of bits, so we need to find the largest number, less than or equal to 23, that is a multiple of 3. That would be 21. So the number of bits for each of the DR, SR1 and SR2 fields is 7.

Thus, the maximum number of registers is:  $2^7 = 128$ .

c) Using the maximum possible number of registers, what is the number of UNUSED bits?

$32 - 9 - (7 \times 3) = 2 \text{ bits}$

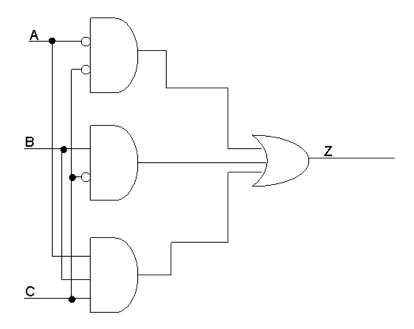

# Problem 3 (4 Points)

The figure below shows a combinational logic circuit. Complete the truth table corresponding to this circuit.

|   | Inputs |   | Inputs Output |  |

|---|--------|---|---------------|--|

| Α | В      | С | Z             |  |

| 0 | 0      | 0 | 1             |  |

| 0 | 0      | 1 | 0             |  |

| 0 | 1      | 0 | 1             |  |

| 0 | 1      | 1 | 0             |  |

| 1 | 0      | 0 | 0             |  |

| 1 | 0      | 1 | 0             |  |

| 1 | 1      | 0 | 1             |  |

| 1 | 1      | 1 | 1             |  |

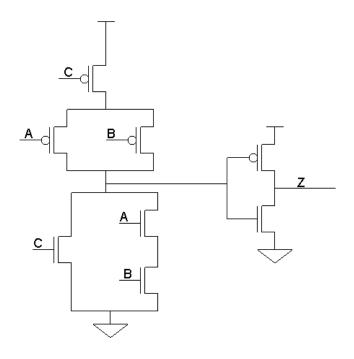

# Problem 4 (4 Points)

Fill in the truth table for the following transistor level circuit. Note that two wires with the same name are assumed to be connected to each other.

|   | Inputs |   |   |

|---|--------|---|---|

| Α | В      | С | Z |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 1 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 1 |

| 1 | 0      | 0 | 0 |

| 1 | 0      | 1 | 1 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 1 |

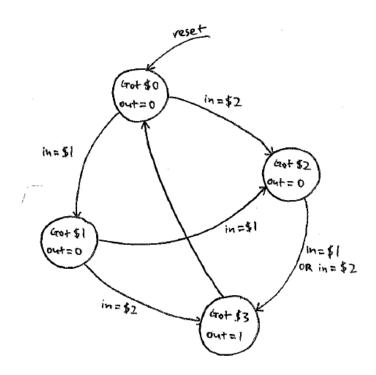

#### **Problem 5 (6 Points)**

A vending machine delivers a package of gum after 3 dollars are deposited. It has a single bill slot which accepts only \$1 or \$2 bills. No other types of bills/coins are accepted. **The vending machine does not return back the change.**

a) Draw the finite state machine (FSM) diagram for the vending machine. The machine takes one input every clock cycle which can be one dollar (\$1), two dollars (\$2), or reset. The machine outputs a '1' when it opens to deliver a gum package, otherwise it outputs a '0'. Assume that once the machine delivers a gum package, it transitions back to the default state (corresponding to no money deposited) in the next clock cycle, regardless of the input.

b) How many flip-flops (storage elements) will be needed to implement this FSM that you designed in your answer to part (a)?

The finite state machine has 4 states. Thus, 2 flip-flops will be needed.

## Problem 6 (4 points)

Circle the correct answer for the following questions:

| Lie the correct answer for the following questions:                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I. A combinational lock requires 4 numbers, entered in a specific sequence, to be unlocked. We can represent this lock as a finite state machine (FSM). What is the minimum number of bits needed to represent the states in the FSM? The output depends only on the current state of the FSM. |

| a. 2                                                                                                                                                                                                                                                                                           |

| b. 3                                                                                                                                                                                                                                                                                           |

| c. 4<br>d. 5                                                                                                                                                                                                                                                                                   |

| u. S                                                                                                                                                                                                                                                                                           |

| b                                                                                                                                                                                                                                                                                              |

| II. Which of the following is <b>not</b> an example of a combinational logic circuit?                                                                                                                                                                                                          |

| a. Decoder                                                                                                                                                                                                                                                                                     |

| b. D-Latch<br>c. Mux (multiplexer)                                                                                                                                                                                                                                                             |

| d. Full adder                                                                                                                                                                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                |

| b                                                                                                                                                                                                                                                                                              |

| III. The minimum number of transistors required to implement a CMOS 3 input NAND gate is                                                                                                                                                                                                       |

| a. 3                                                                                                                                                                                                                                                                                           |

| b. 8                                                                                                                                                                                                                                                                                           |

| c. 6                                                                                                                                                                                                                                                                                           |

| d. 4                                                                                                                                                                                                                                                                                           |

| c                                                                                                                                                                                                                                                                                              |

| IV. If a memory uses 8-bit words and 8-bit addressing, how many D-Latches are needed for the memory?                                                                                                                                                                                           |

| a. 4096                                                                                                                                                                                                                                                                                        |

| b. 1024                                                                                                                                                                                                                                                                                        |

| c. 2048                                                                                                                                                                                                                                                                                        |

| d. 8192                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                |

| a or c. If you assumed that the memory is represented by one flip-flop for each bit,                                                                                                                                                                                                           |

the answer is a, since there are two D-Latches in a single flip-flop. Otherwise, if you assumed that the memory is represented by one D-Latch for each bit, the answer is c.