# LC-3 Datapath

ECE/CS 252, Fall 2010

Prof. Mikko Lipasti

Department of Electrical and Computer Engineering

University of Wisconsin – Madison

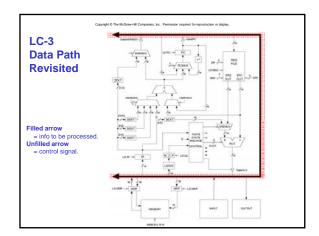

#### Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display. **Data Path Components** Output Global bus · special set of wires that carry a 16-bit signal to many components · inputs to the bus are "tri-state devices," Enable that only place a signal on the bus when they are enabled Input • only one (16-bit) signal should be enabled at any time > control unit decides which signal "drives" the bus · any number of components can read the bus > register only captures bus data if it is write-enabled by the control unit

Data Path Components

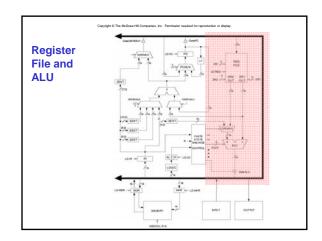

ALU

Accepts inputs from register file and from sign-extended bits from IR (immediate field).

Output goes to bus.

> used by condition code logic, register file, memory

Register File

Two read addresses (SR1, SR2), one write address (DR)

Input from bus

> result of ALU operation or memory read

Two 16-bit outputs

> used by ALU, PC, memory address

> data for store instructions passes through ALU

Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or disp

#### **Data Path Components**

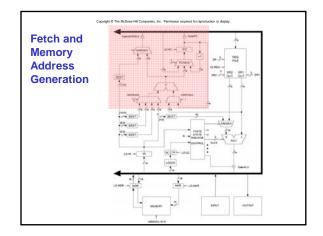

#### PC and PCMUX

- Three inputs to PC, controlled by PCMUX

- 1. PC+1 FETCH stage

- 2. Address adder BR, JMP

- 3. bus TRAP (discussed later)

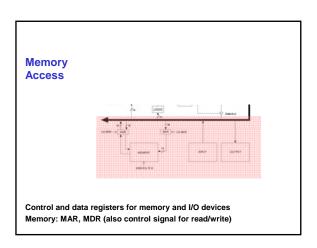

#### MAR and MARMUX

- Two inputs to MAR, controlled by MARMUX

- 1. Address adder LD/ST, LDR/STR

- 2. Zero-extended IR[7:0] -- TRAP (discussed later)

Condition

Code Logic

and Control

Unit

Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or disp

## **Data Path Components**

## **Condition Code Logic**

- Looks at value on bus and generates N, Z, P signals

- Registers set only when control unit enables them (LD.CC)

Fonly certain instructions set the codes (ADD, AND, NOT, LD, LDI, LDR, LEA)

# Control Unit - Finite State Machine

- On each machine cycle, changes control signals for next phase of instruction processing

- >who drives the bus? (GatePC, GateALU, ...)

- $\blacktriangleright$  which registers are write enabled? (LD.IR, LD.REG, ...)

- > which operation should ALU perform? (ALUK)

- >...

- Logic includes decoder for opcode, etc.

Copyright © The McGraw-Hill Companies, Inc. Permission required for reproduction or display

#### **Summary**

# LC-3 Data Path

- Global Bus

- Memory Interface

- Register File and ALU

- · Fetch and Memory Address Generation

- Condition Code Logic

- Control Unit

Just one way to build the data path for this ISA Alternatives may:

- Consume less power

- · Provide better performance, clock frequency